计算机组成

Table of Contents

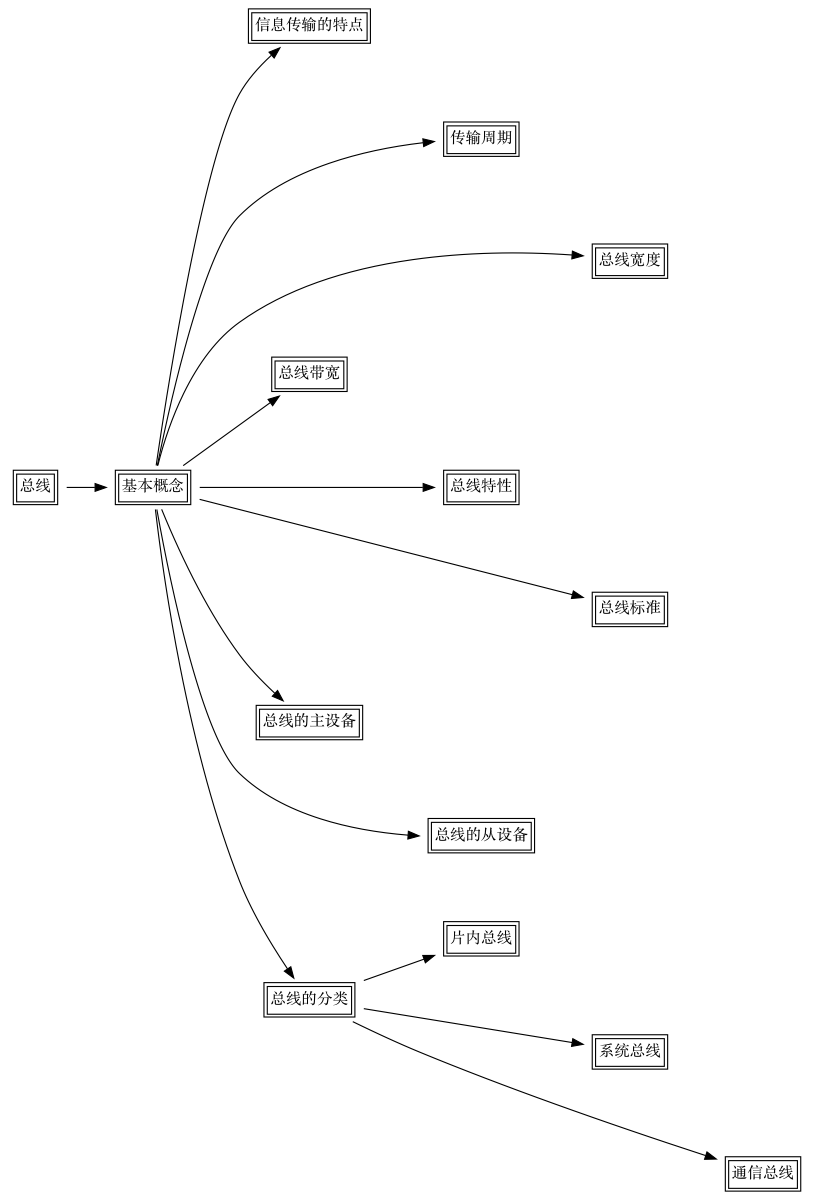

1 总线

1.1 基本概念

| 概念 | 含义 |

|---|---|

| 传输特点 | 共享的传输介质,某时刻仅允许一个部件向总线发送,但多个部件可获取 |

| 传输周期 | 完成一次总线操作的时间,包括申请阶段、寻址阶段、传送阶段和结束阶段 |

| 总线宽度 | 总线上能同时传输的数据位数–总线根数 |

| 总线带宽 | 单位时间内总线上传输数据的位数,通常用每秒钟传送信息的字节数来衡量 |

| 总线特性 | 机械特性、电气特性、功能特性和时间特性 |

| 总线标准 | 国际公布或推荐的互联各个模块的标准。 |

| 总线的主设备 | 获得总线控制权的设备 |

| 总线的从设备 | 被主设备访问的设备,只能响应从主设备发来的各种总线命令。 |

| 片内总线 | 芯片内的总线 |

| 系统总线 | 连接CPU、主存、I/O设备各部件间的信息传输线。 |

| 通信总线 | 链接计算机间或计算机系统间的信息传输线 |

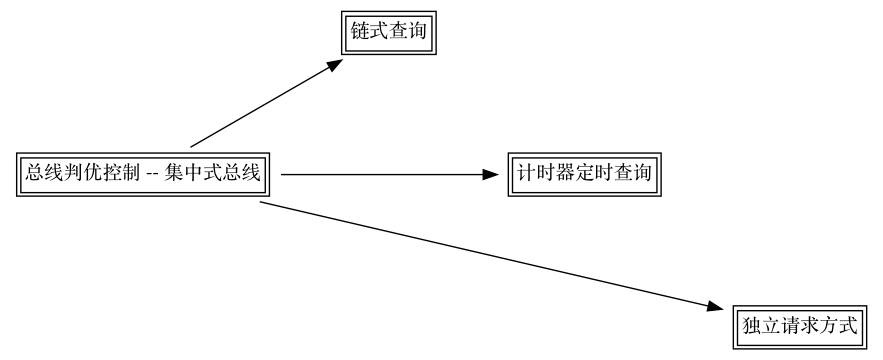

1.2 总线判优控制

| 概念 | 含义 |

|---|---|

| 链式查询 | BS-总线忙;BR-总线请求;BG-总线同意。BG信号串式地从一个I/O接口传送到下一个I/O接口 |

| 计数器定时查询 | 相对上者,少了BG线。多了一组设备地址线。当BS=0(总线不忙)接收到BR信号后,则计数器开始计数,并通过地址线发出一组地址信号。 |

| 独立请求方式 | 每一组设备都有一组独立的BR/BG线。控制芯片内一般有排队电路。 |

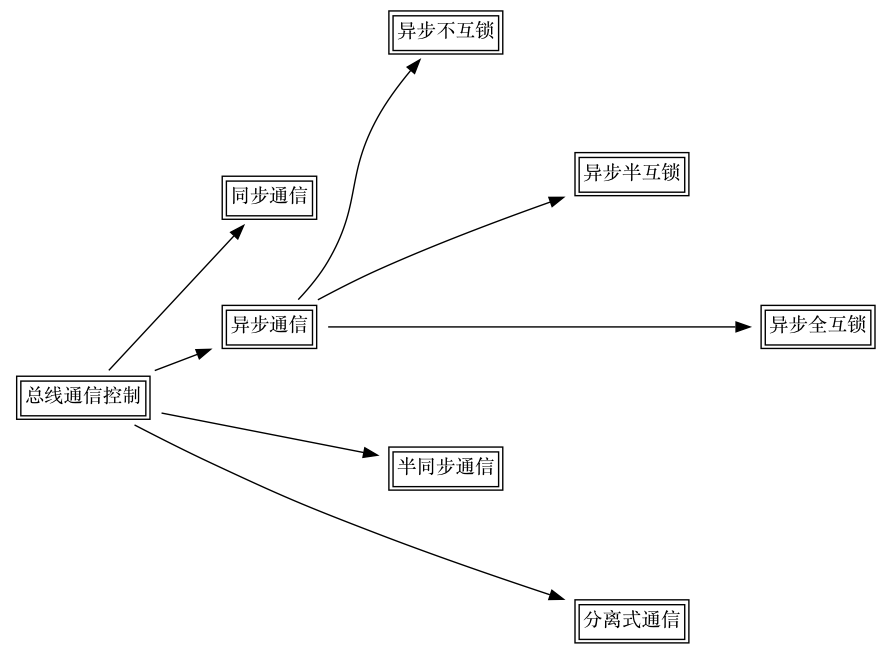

1.3 总线通信控制

主要解决通信双方如何获知传输开始和传输结束,以及通信双方如何协调如何配合。

| 通信方式 | 描述 | 优点 | 缺点 | |

|---|---|---|---|---|

| 同步通信 | 通信双方由统一时标控制数据传送。 | 规定明确、统一、模块间的配合简单一致。 | 主、从模块时间配合属于强制性“同步”,必须在限定时间内完成规定的操作。 | |

| 异步通信 | 应答方式(握手方式),主模块发出"请求"(Request)时,待从模块的"响应"(Acknowledge)信号。需要添加应答线。 | 模块毋需速度一致 | 设计较同步通信复杂 | |

| 异步不互锁 | 主模块发出"请求"信号后,不需等待从模块发回"响应"信号,即可撤除"请求"信号。 – CPU -> 主存 | |||

| 异步半互锁 | 主模块发出"请求"信号后,需要等待从模块发回"响应"信号,才可撤除"请求"信号。 – CPU访问共享存储器-必须确认共享的存储器未被占用 | |||

| 异步全互锁 | 主模块发出"请求"信号后,等待从模块发回"响应"信号,才撤除"请求"信号。从模块也需主模块以取消"请求"信号后后,才可取消"响应"。 | |||

| 半同步通信 | 地址、命令、数据信号的发出时间,严格按照系统时钟的某个前沿开始,接收方则都采用系统时钟后沿时刻来进行判断识别。增加"等待"(Wait)线 | 比异步通信简单。可靠性高,各模块工作于统一时钟控制下。 | 系统时钟频率不能太高,适合于较慢的系统 | |

| 分离式通信 | P65看书,其实说白了就是每个模块都是主模块。若要进行数据传送,则需要主动申请主线的使用权。 | 不存在空闲的主线占用时间,利用率高。 | 控制复杂。 |